# MN83901ABG-C

## LCD Panel Source Driver

### Overview

The MN83901ABG-C is an LCD panel source driver that can display an analog video signal on a color TFT LCD panel in products such as LCD TV sets and camcorders.

#### Features

- Number of driver outputs: 240 outputs

- Lower power consumption and lower EMI due to a 2.7 to 5.5 V digital power supply system and a 5.0 V analog power supply system.

- Wide dynamic range: 4.6 V (at supply voltage: 5.0 V)

- Low inter-pin variation between output pins: ±20 mV (typical)

- Provides analog RGB signal switching to support both stripe and delta color filter arrays.

- Mode input selects between sequential sampling (CLK1, CLK2, and CLK3 input) and simultaneous sampling (CLK1 input, with CLK2 and CLK3 held at V<sub>DD1</sub>).

- Schmitt trigger circuit minimizes noise on the OE pin.

- Supports serial cascade connection.

- The clock is automatically stopped after a fixed amount of data is acquired.

- Bidirectional shift register

- Supports mounting in thin-frame panels. (The chip short side length is under 1 mm.)

- Package type: bare chip

#### Applications

• LCD panel driver for LCD TVs and camcorders

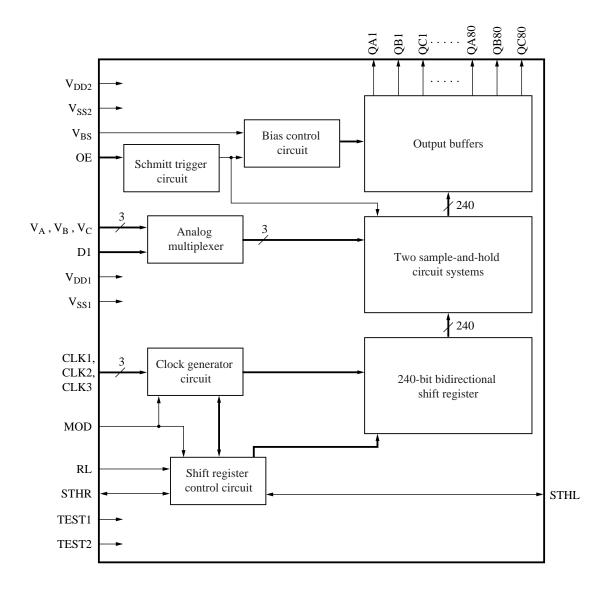

## Block Diagram

## Pin Descriptions

| Pin Name        | I/O | Function                    | Description                                                 |                                                                                                                                                                                                                            |                                                                                                                                                   |  |  |  |

|-----------------|-----|-----------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

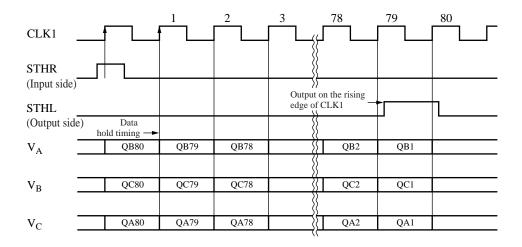

| STHR<br>STHL    | I/O | Shift data input and output | shift regis                                                 |                                                                                                                                                                                                                            | data handled by the bidirectional<br>output functions are switched by                                                                             |  |  |  |

|                 |     |                             | RL                                                          | STHR                                                                                                                                                                                                                       | STHL                                                                                                                                              |  |  |  |

|                 |     |                             | High                                                        | Ι                                                                                                                                                                                                                          | 0                                                                                                                                                 |  |  |  |

|                 |     |                             | Low                                                         | 0                                                                                                                                                                                                                          | I                                                                                                                                                 |  |  |  |

|                 |     |                             | This da<br>edge of<br>2) Output<br>Output<br>connec         | tta is acquired in<br>CLK1.<br>s data for input to t<br>ted in cascade (seri<br>ta is output in sync                                                                                                                       | stage of the shift register.<br>synchronization with the rising<br>the next stage when this IC is<br>ies).<br>chronization with the rising edge   |  |  |  |

| RL              | Ι   | Shift direction selection   |                                                             |                                                                                                                                                                                                                            | irection of the bidirectional shift                                                                                                               |  |  |  |

|                 |     |                             | register.<br>RL = h                                         | igh : $QA1 \rightarrow QB1$                                                                                                                                                                                                | $\rightarrow QC1 \cdots \rightarrow QC80$ $80 \rightarrow QA80 \cdots \rightarrow QA1$                                                            |  |  |  |

| CLK1 to<br>CLK3 | Ι   | Clock inputs                | output to<br>relation b<br>1) MOD =<br>CLK1<br>CLK2<br>CLK3 | the LCD drive out<br>etween these clock<br>= low (Sequential s<br>RL = high : QA1<br>RL = low : QC1<br>: QB1<br>RL = high : QC1<br>RL = low : QA1<br>= high (Simultaneous)<br>: QA1 t<br>: QB1 t<br>: QC1 t<br>: Conneous) | to QA80<br>to QC80<br>to QB80<br>to QC80                                                                                                          |  |  |  |

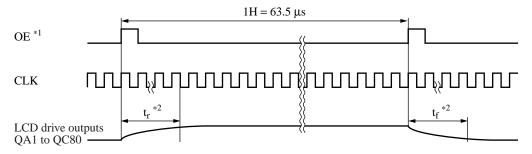

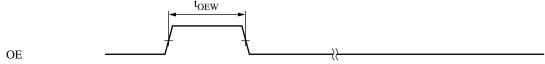

| OE              | I   | Output enable               | The rising<br>and-hold<br>When the                          | edge of this signal<br>circuit systems and<br>output reaches th<br>ally lowered, and a                                                                                                                                     | switches between the two sample-<br>l starts the output of new data.<br>e drive potential, the capacity is<br>t the same time the drive potential |  |  |  |

## ■ Pin Descriptions (continued)

| Pin Name                                           | I/O | Function                                   |                             | D                                  | escription                                                                                              |

|----------------------------------------------------|-----|--------------------------------------------|-----------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------|

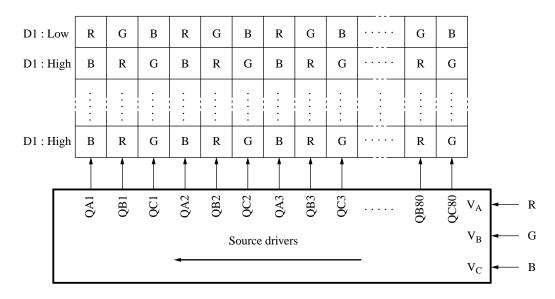

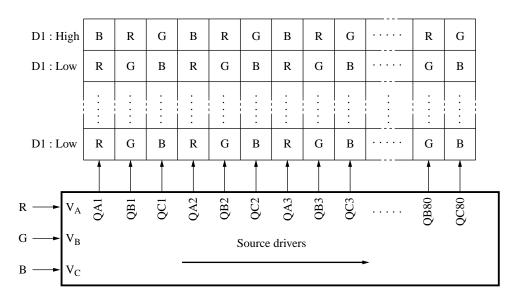

| D1                                                 | Ι   | Analog signal switching                    |                             |                                    | input signals $V_A$ , $V_B$ , and $V_C$ , the QA, QB, and QC outputs.                                   |

|                                                    |     |                                            | D1                          | I                                  | 0                                                                                                       |

|                                                    |     |                                            | Low                         | V <sub>A</sub>                     | QA1 to QA80                                                                                             |

|                                                    |     |                                            |                             | V <sub>B</sub>                     | QB1 to QB80                                                                                             |

|                                                    |     |                                            |                             | V <sub>C</sub>                     | QC1 to QC80                                                                                             |

|                                                    |     |                                            | High                        | V <sub>A</sub>                     | QB1 to QB80                                                                                             |

|                                                    |     |                                            |                             | V <sub>B</sub>                     | QC1 to QC80                                                                                             |

|                                                    |     |                                            |                             | V <sub>C</sub>                     | QA1 to QA80                                                                                             |

| V <sub>BS</sub>                                    | Ι   | Bias adjustment                            | -                           |                                    | s pin adjusts the output buffer<br>e capacity of the LCD drive outputs                                  |

| V <sub>A</sub><br>V <sub>B</sub><br>V <sub>C</sub> | Ι   | Analog signal inputs                       | Inputs for t<br>drive outpu |                                    | als for output from the LCD                                                                             |

| QA1 to QA80<br>QB1 to QB80<br>QC1 to QC80          | 0   | LCD drive outputs                          |                             |                                    | $V_A$ , $V_B$ , or $V_C$ are sampled and output from these pins.                                        |

| MOD                                                | Ι   | Mode selection input                       | $V_A, V_B, and MOD = 1$     | d V <sub>C</sub> is perform        | ling of the 3 analog input signals<br>ned simultaneously or sequentially<br>eous sampling<br>l sampling |

| TEST1                                              | Ι   | Test input                                 | Connect to                  | V <sub>DD1</sub> .                 |                                                                                                         |

| TEST2                                              | Ι   | Test input                                 | Connect to                  | V <sub>DD1</sub> .                 |                                                                                                         |

| V <sub>DD1</sub>                                   |     | Digital system high potential power supply | High-level                  | side of the dig                    | ital (logic) system power supply                                                                        |

| V <sub>DD2</sub>                                   |     | Analog system high potential power supply  | -                           | side of the ana<br>-and-hold and o | log system power supply used other circuits                                                             |

| V <sub>SS1</sub>                                   |     | Digital system ground                      | Digital syst                | tem ground use                     | ed for logic and other circuits                                                                         |

| V <sub>SS2</sub>                                   |     | Analog system ground                       | Analog sys<br>other circui  | -                                  | ed for sample-and-hold and                                                                              |

## Functional Description

### 1. Output signals

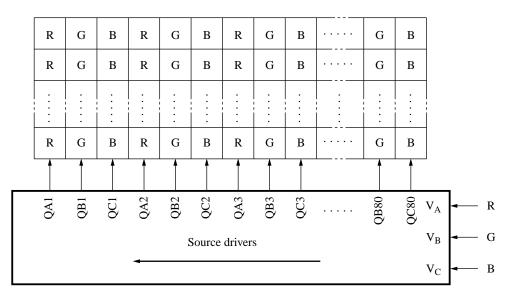

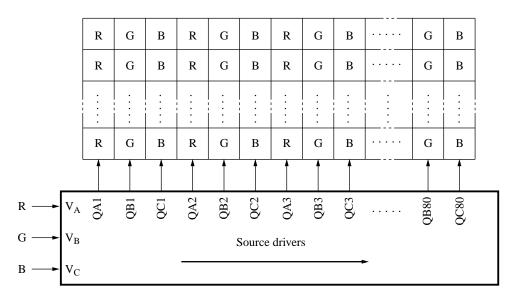

The MN83901ABG-C supports both stripe and delta color filter arrangement LCD panels. The relationship between the input pins and the output pins is switched by the DI pin.

- 1) Stripe arrangement

- Left-shift mode (RL = low), DI = low

• Right-shift mode (RL = high), DI = low

- Functional Description (continued)

- 1. Output signals (continued)

- 2) Delta arrangement

- Left-shift mode (RL = low)

• Right-shift mode (RL = high)

- Functional Description (continued)

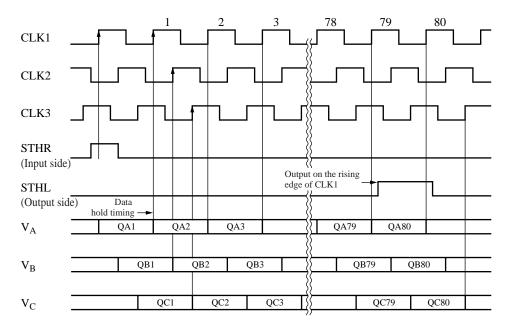

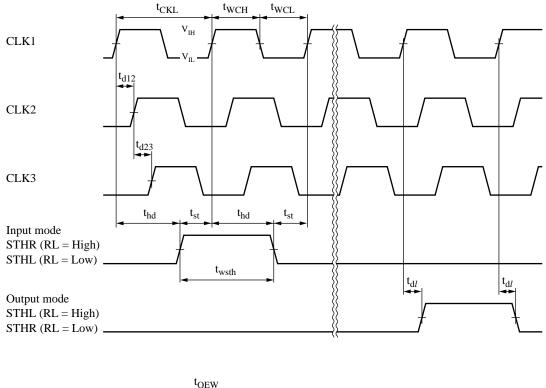

- 2. Recommended operating timing diagrams

- 1)  $QA1 \rightarrow QC80$  transfer mode: DI = low, MOD = low

- Sequential sampling mode

• Start of sampling

When CLK1 rises, the start pulse (STHR = high) is acquired and sampling of the analog signal QA1 starts. The analog signal QA1 is held on the next CLK1 rising edge.

· Auto standby function

After sampling the analog signal QC80, the IC automatically goes to the standby state, the shift register is reset, and sampling is not performed until a high level is input to STHR again.

When multiple start pulses are input, although all the start pulses are transmitted to the shift register, the IC goes to the standby state 81 clock cycles after the first start pulse.

- Note) \*1: The rising edge of this signal switches between the two sample-and-hold circuit systems and starts the output of new data. When the output reaches the drive potential, the capacity is automatically lowered, and at the same time the drive potential is held steady.

- \*2: The settling time is adjusted with  $V_{BS}$ .

- Functional Description (continued)

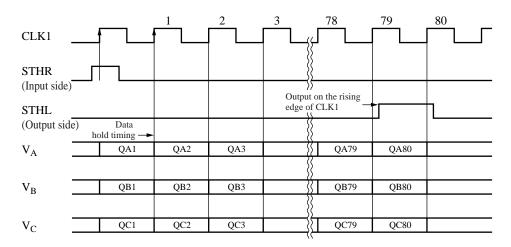

- 2. Recommended operating timing diagrams (continued)

- 2)  $QA1 \rightarrow QC80$  transfer mode: DI = low, MOD = high

- Simultaneous sampling mode (Connect CLK2 and CLK3 to V<sub>DDI</sub>.)

3) QC80  $\rightarrow$  QA1 transfer mode: DI = high, MOD = high

• Simultaneous sampling mode (Connect CLK2 and CLK3 to V<sub>DDI</sub>.)

## Functional Description (continued)

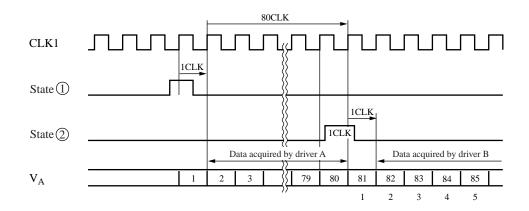

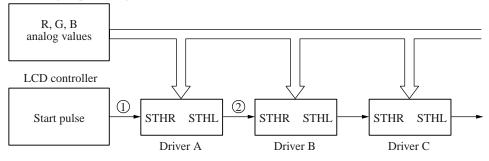

- 3. Operation when cascade connection is used

- When RL is high

When a start pulse is input to STHR, after one clock (CLK) cycle passes, driver A starts to acquire data. STHL (carry output) rises 80 clock cycles after the start pulse input, and one clock cycle later, data acquisition stops. Driver B accepts the driver A STHL output as a start pulse input, and starts data acquisition one clock cycle later.

Chromatic signal processing IC

#### Electrical Characteristics

| 1. | Absolute | Maximum | Ratings at | $V_{SS1} = 0$ | $V, V_{SS2} = 0$ | V |

|----|----------|---------|------------|---------------|------------------|---|

|----|----------|---------|------------|---------------|------------------|---|

| Item                                    | Symbol           | Rating                         | Unit |

|-----------------------------------------|------------------|--------------------------------|------|

| Digital system supply voltage           | V <sub>DD1</sub> | – 0.3 to +7.0                  | V    |

| Analog system supply voltage            | V <sub>DD2</sub> | - 0.3 to +7.0                  | V    |

| Digital input voltage                   | V <sub>I1</sub>  | - 0.3 to V <sub>DD1</sub> +0.3 | V    |

| Analog input voltage                    | V <sub>I2</sub>  | - 0.3 to V <sub>DD2</sub> +0.3 | V    |

| Digital output voltage                  | V <sub>01</sub>  | – 0.3 to V <sub>DD1</sub> +0.3 | V    |

| Analog output voltage                   | V <sub>O2</sub>  | - 0.3 to V <sub>DD2</sub> +0.3 | V    |

| Operating and storage temperature range | Ta               | -30 to +85                     | °C   |

| Operating temperature                   | T <sub>opr</sub> | -20 to +75                     | °C   |

| Storage temperature                     | T <sub>stg</sub> | -40 to +110                    | °C   |

Note) 1. The absolute maximum ratings are limit values for stresses applied to the chip so that the chip will not be destroyed. Operation is not guaranteed within these ranges.

Also, the operating and storage temperature range is the temperature range over which the IC may be operated without damage to the IC. IC performance is not guaranteed within this range.

2. These ratings are guaranteed values when the standard Panasonic package is used.

#### 2. Operating Conditions at $V_{SS1} = 0$ V, $V_{SS2} = 0$ V, $T_a = -20^{\circ}C$ to $+75^{\circ}C$

| Item                                    | Symbol               | Condition                | Min | Тур | Max             | Unit |

|-----------------------------------------|----------------------|--------------------------|-----|-----|-----------------|------|

| Operating digital system supply voltage | V <sub>DD1</sub>     |                          | 2.7 | 3.0 | 5.5             | V    |

| Operating analog system supply voltage  | V <sub>DD2</sub>     |                          | 4.5 | 5.0 | 5.5             | V    |

| Analog reference voltage                | V <sub>BS</sub>      |                          | 1.0 | 2.0 | 3.0             | V    |

| Operating frequency                     | f <sub>clk</sub>     |                          | 0.5 |     | 15              | MHz  |

| Analog input voltage                    | $V_{IA}$ to $V_{IC}$ |                          | 0.2 | —   | $V_{DD2} - 0.2$ | V    |

| Drive output load capacitance           | C <sub>Y</sub>       |                          | _   | —   | 100             | pF   |

| Digital signal input pin capacitance    | C <sub>inD</sub>     | For a 1 MHz input signal | _   | 8   | 20              | pF   |

| Analog signal input pin capacitance     | C <sub>inA</sub>     | For a 1 MHz input signal | _   | 10  | 20              | pF   |

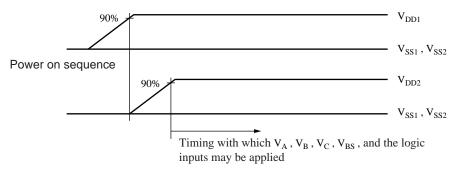

Note) 1. The multiple V<sub>DD1</sub> and V<sub>DD2</sub> power supply pins must all be connected to the power supply level.

2. The multiple  $V_{SS1}$  and  $V_{SS2}$  ground pins must all be connected to ground.

3. When powering on this IC, first apply V<sub>DD1</sub> and V<sub>DD2</sub>, and only then apply V<sub>A</sub>, V<sub>B</sub>, V<sub>C</sub>, V<sub>BS</sub>, and the logic inputs. When power down this IC, use the reverse sequence from the power on sequence.

- 4. The operating supply voltages are the voltages applied to  $V_{DD1}$  and  $V_{DD2}$ .

- 5. These ratings are guaranteed values when the standard Panasonic package is used.

## Electrical Characteristics (continued)

| 3. | DC Characteristics (continued) at VDD | $_{1}$ = 2.7 V to 5.5 V, V <sub>DD2</sub> = 5.0 V, V <sub>SS</sub> | $_{SS1} = V_{SS2} = 0 \text{ V}, \text{ V}_{BS} = 2.5 \text{ V}, \text{ f}_{clk} = 15 \text{ MH}$ | z, T <sub>a</sub> = 25°C |

|----|---------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|

|----|---------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|

| Item                                            | Symbol               | Condition                                                                                                                                       | Min                  | Тур | Max                  | Unit |

|-------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|----------------------|------|

| Operating analog system supply current 1 *1,2,3 | I <sub>DD1</sub>     |                                                                                                                                                 |                      | 4.5 | 10                   | mA   |

| Operating analog system supply current 2 *3, 4  | I <sub>DD2</sub>     | With no load                                                                                                                                    |                      | 3.5 |                      | mA   |

| Operating digital system supply current *1      | I <sub>DD3</sub>     |                                                                                                                                                 | _                    | 2.3 | 6.5                  | mA   |

| Quiescent digital system supply current         | I <sub>DD4</sub>     | In the clock stopped state                                                                                                                      |                      |     | 100                  | μA   |

| 1) Input pins: RL, CLK1, D1                     |                      |                                                                                                                                                 |                      |     |                      |      |

| High-level input voltage                        | $V_{\rm IH1}$        |                                                                                                                                                 | $0.7 \times V_{DD1}$ |     | V <sub>DD1</sub>     | V    |

| Low-level input voltage                         | $V_{IL1}$            |                                                                                                                                                 | 0                    | —   | $0.3 \times V_{DD1}$ | V    |

| Input leakage current                           | $V_{LI1}$            |                                                                                                                                                 | -10                  |     | 10                   | μA   |

| 2) Schmitt trigger input pins: O                | Е                    | •                                                                                                                                               |                      |     |                      |      |

| High-level input voltage                        | V <sub>IH2</sub>     |                                                                                                                                                 | $0.8 \times V_{DD1}$ |     | V <sub>DD1</sub>     | V    |

| Low-level input voltage                         | V <sub>IL2</sub>     |                                                                                                                                                 | 0                    |     | $0.2 \times V_{DD1}$ | V    |

| Schmitt voltage                                 | $\Delta V_{smt}$     | $V_{DD1} = 3.3 V$                                                                                                                               | _                    | 0.5 | _                    | V    |

| Input leakage current                           | V <sub>LI2</sub>     |                                                                                                                                                 | -10                  |     | 10                   | μA   |

| 3) Conditional (when MOD is h                   | nigh) pull-up        | resistor input pins: CL                                                                                                                         | K2, CLK3             |     |                      |      |

| High-level input voltage                        | V <sub>IH3</sub>     |                                                                                                                                                 | $0.7 \times V_{DD1}$ |     | V <sub>DD1</sub>     | V    |

| Low-level input voltage                         | V <sub>IL3</sub>     |                                                                                                                                                 | 0                    |     | $0.3 \times V_{DD1}$ | V    |

| Pull-up resistance                              | R <sub>PU3</sub>     | $V_{DD1} = 3.6 V$                                                                                                                               | 1.5                  | 5   | 15                   | kΩ   |

| 4) Pull-up resistor input pins: 7               | TEST1, TEST          | 2                                                                                                                                               |                      |     |                      |      |

| High-level input voltage                        | $V_{IH4}$            |                                                                                                                                                 | $0.7 \times V_{DD1}$ |     | V <sub>DD1</sub>     | V    |

| Low-level input voltage                         | V <sub>IL4</sub>     |                                                                                                                                                 | 0                    |     | $0.3 \times V_{DD1}$ | V    |

| Pull-up resistance                              | R <sub>PU4</sub>     | $V_{DD1} = 3.6 V$                                                                                                                               | 1.5                  | 5   | 15                   | kΩ   |

| 5) Pull-down resistor input pin                 | s: MOD               | ·                                                                                                                                               | · · · ·              |     |                      |      |

| High-level input voltage                        | V <sub>IH5</sub>     |                                                                                                                                                 | $0.7 \times V_{DD1}$ |     | V <sub>DD1</sub>     | V    |

| Low-level input voltage                         | V <sub>IL5</sub>     |                                                                                                                                                 | 0                    |     | $0.3 \times V_{DD1}$ | V    |

| Pull-down resistance                            | R <sub>PU5</sub>     | $V_{DD1} = 3.6 V$                                                                                                                               | 30                   | 100 | 300                  | kΩ   |

| 6) I/O pins: STHR, STHL                         |                      |                                                                                                                                                 |                      |     |                      |      |

| High-level input voltage                        | $V_{IH6}$            |                                                                                                                                                 | $0.7 \times V_{DD1}$ |     | V <sub>DD1</sub>     | V    |

| Low-level input voltage                         | V <sub>IL6</sub>     |                                                                                                                                                 | 0                    |     | $0.3 \times V_{DD1}$ | V    |

| High-level output voltage                       | V <sub>OH</sub>      | $I_0 = -1 \text{ mA}$                                                                                                                           | $V_{DD1} - 0.1$      | —   | —                    | V    |

| Low-level output voltage                        | V <sub>OL</sub>      | $I_0 = 1 \text{ mA}$                                                                                                                            | _                    |     | 0.1                  | V    |

| 7) Analog input pins: $V_A$ , $V_B$ ,           | V <sub>C</sub>       |                                                                                                                                                 |                      |     |                      |      |

| Input current                                   | $I_{VA}$ to $I_{VC}$ | Analog input<br>$(V_A, V_B, V_C)$<br>frequency = 0.5 MHz<br>Analog input $(V_A, V_B, V_C)$<br>$V_C$ ) amplitude =<br>$(V_{DD2} - 0.2)$ to 0.2 V | -150                 |     | 150                  | mA   |

#### Electrical Characteristics (continued)

| 3. | DC Characteristics (continued) at V <sub>DD1</sub> | = 2.7 V to 5.5 V, $V_{DD2}$ = 5.0 V, $V_{SS}$ | $_{S1} = V_{SS2} = 0 V, V_{BS} = 2.5 V, f_{clk} =$ | = 15 MHz, T <sub>a</sub> = 25°C |

|----|----------------------------------------------------|-----------------------------------------------|----------------------------------------------------|---------------------------------|

|----|----------------------------------------------------|-----------------------------------------------|----------------------------------------------------|---------------------------------|

| Item                                     | Symbol             | Condition                                                                                                                      | Min  | Тур  | Max | Unit |

|------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| 8) Reference voltage input pir           | ו: V <sub>BS</sub> |                                                                                                                                |      |      |     |      |

| Input leakage current                    | I <sub>VBS</sub>   |                                                                                                                                | -10  | _    | 10  | mA   |

| 9) Analog output pins: QA1 to            | QC80               |                                                                                                                                |      |      | ·   |      |

| Output current                           | I <sub>OH</sub>    | Analog input voltage<br>$(V_A, V_B, V_C) = 4.8 V$<br>Output pin applied voltage<br>(QA1  to  QC80) = 3.8 V<br>$V_{BS} = 2.7 V$ | 0.03 | 0.05 |     | mA   |

|                                          | I <sub>OL</sub>    | Analog input voltage<br>$(V_A, V_B, V_C) = 0.2 V$<br>Output pin applied voltage<br>(QA1  to  QC80) = 1.2 V                     | 0.15 | 2    |     | _    |

| Inter-pin output voltage<br>deviation *5 | $\Delta V_{0}$     |                                                                                                                                | _    | ±20  |     | mV   |

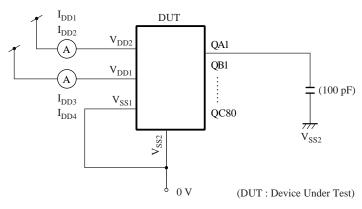

#### Note) 1. \*1: Load conditions

Analog input signals ( $V_A$ ,  $V_B$ ,  $V_C$ ) = 7.5 MHz, amplitude = 0.2 V to 4.8 V, OE = 100 kHz,  $V_{BS}$  = 2.5 V

- \*2: The load on the analog output pins (QA1 to QC80) changes in certain cases.

- \*3: The formula for calculating the power consumption when a load is connected is as follows.

- $I_{DD1} \times V_{DD2} + I_{DD3} \times V_{DD1}$

Use the value for  $I_{DD2}$  for  $I_{DD1}$  in the formula above to calculate the power consumption when there is no load.

- \*4: The no load power consumption value is provided for reference purposes only; this value is not guaranteed.

- \*5: V<sub>OUT</sub> expresses the output voltage for each output pin, whereas V<sub>MAX</sub> and V<sub>MIN</sub> express the maximum and minimum values for the output voltage for the chip-internal output terminals.

- 2. These ratings are guaranteed values when the standard Panasonic package is used.

#### Electrical Characteristics (continued)

#### 4. AC Characteristics at $V_{DD1} = 2.7$ V to 5.5 V, $V_{DD2} = 5.0$ V, $V_{SS1} = V_{SS2} = 0$ V, $T_a = 25^{\circ}C$

| DDT                                       |                       | ; DD2 ; 001       | 002  | , u |                       |      |

|-------------------------------------------|-----------------------|-------------------|------|-----|-----------------------|------|

| Item                                      | Symbol                | Condition         | Min  | Тур | Max                   | Unit |

| Clock cycle time                          | t <sub>CLK</sub>      |                   | 66.6 | —   | 2 000                 | ns   |

| Clock high-level period                   | t <sub>WCH</sub>      |                   | 27   | —   | —                     | ns   |

| Clock low-level period                    | t <sub>WCL</sub>      |                   | 27   |     | _                     | ns   |

| Clock delay time                          | $t_{d12}$ , $t_{d23}$ |                   | 16.6 | _   | t <sub>CLK</sub> /2   | ns   |

| Start pulse setup time                    | t <sub>st</sub>       |                   | 10   | —   | t <sub>CLK</sub> –5   | ns   |

| Start pulse hold time                     | t <sub>hd</sub>       |                   | 5    | _   | t <sub>CLK</sub> -10  | ns   |

| Start pulse width                         | t <sub>wsth</sub>     |                   | 15   | _   | 2t <sub>CLK</sub> -15 | ns   |

| Carry signal output delay time            | t <sub>dl</sub>       | With a 25 pF load | 5    |     | 56                    | ns   |

| Output switching signal high-level period | t <sub>OEW</sub>      |                   | 1    | —   | _                     | μs   |

Note) These ratings are guaranteed values when the standard Panasonic package is used.

#### • Sequential sampling mode

Note) In simultaneous sampling mode, both CLK2 and CLK3 are held fixed at the high level.

## Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

## Please read the following notes before using the datasheets

- A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use. Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.